Q

# High-Speed CMOS 512/1K/2K/4K x 9 Parallel Clocked FIFO

QS72211 QS72221 QS72231 QS72241

## **FEATURES**

- 512 x 9 (QS72211)

- 1K x 9 (QS72221)

- 2K x 9 (QS72231)

- 4K x 9 (QS72241)

- Ultra-high speed 12-ns (83 MHz) read/write cycle times

- · Synchronous/asynchronous read and write

- · Industry-standard pinouts

- · Four flag signals

- Empty flag

- Full flag

- Programmable Almost-Empty flag defaults to EMPTY+7

- Programmable Almost-Full flag defaults to FULL-7

- Output Enable (OE) pin

- · Available in 32-pin PLCC

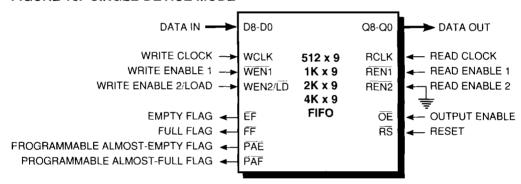

# DESCRIPTION

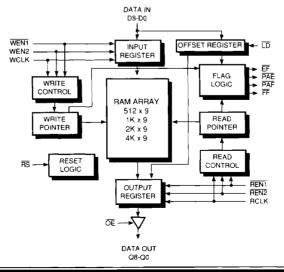

The QS72211/221/231/241 are high-speed 512/1K/ 2K/4Kx9parallel, clocked FIFOs, respectively. These FIFOs have 9-bit input and output ports. The input port is controlled by a free running clock (WCLK) and two write enable pins (WEN1, WEN2). The output port is controlled by another clock pin (RCLK) and two read enable pins (REN1, REN2). An output enable pin (OE) is provided on the read port for HIGH-Z control of the output. These FIFOs also have two fixed flags. Empty (EF) and Full (FF), which prevent the FIFO from being written into when full or being read from when empty. There are two additional programmable flags. Almost-Empty flag (PAE) and Almost-Full flag (PAF) for improved system control. The programmable flags default to EMPTY+7 and FULL-7 for PAE and PAF, respectively. The programmable flag offset loading is controlled by asserting the load pin  $(\overline{LD})$ . These FIFOs are easily cascadable to any depth and expandable to any width without any speed penalty and are useful for data communications, digital filtering, processor communication, and video line-doubling applications.

### FIGURE 1. FUNCTIONAL BLOCK DIAGRAM

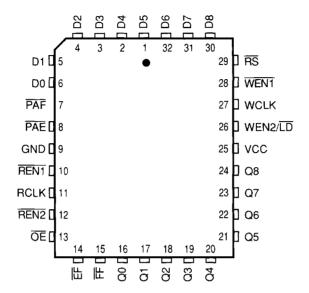

FIGURE 2. QS722X1 PINOUT, 32-PIN PLCC (All pins top view)

# **TABLE 1. PIN DESCRIPTIONS**

| Name         | I/O | Function                             | Description                                                                                                                                                                                                                                                                                         |

|--------------|-----|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D8-D0        | - 1 | Data Inputs                          | Nine inputs for the memory array or offset registers.                                                                                                                                                                                                                                               |

| PAÉ          | 0   | Programmable<br>Almost-Empty<br>Flag | When the signal goes LOW, it indicates the array is almost empty, based on the offset value in the almost-empty offset registers. The default value is EMPTY+7. PAE transition is synchronous with RCLK.                                                                                            |

| PAF          | 0   | Programmable<br>Almost-Full<br>Flag  | When the signal goes LOW, it indicates the array is almost full, based on the offset value in the almost-full offset registers. The default value is FULL-7. PAF transition is synchronous with WCLK.                                                                                               |

| RCLK         |     | Read Clock                           | Data are read from the FIFO when REN1 and REN2 are LOW on the rising edge of RCLK. The EF and PAE transitions are synchronized to the RCLK.                                                                                                                                                         |

| REN1<br>REN2 | 1   | Read Enable                          | When REN1 and REN2 are LOW on the rising edge of RCLK, data will be read from the FIFO.                                                                                                                                                                                                             |

| ŌĒ           | 1   | Output Enable                        | The outputs are in an active state when $\overline{OE}$ is LOW. If $\overline{OE}$ is HIGH, the outputs will be in the high-impedance state.                                                                                                                                                        |

| EF           | 0   | Empty Flag                           | The EF is LOW when the array is empty and further data reads are inhibited. The EF is synchronized to RCLK. When EF is HIGH, the FIFO is not empty, and the data can be read from the FIFO.                                                                                                         |

| FF           | 0   | Full Flag                            | The FF is LOW when the array is full and further data writes are inhibited. The FF is synchronized to WCLK. When FF is HIGH, data can be written into the FIFO until the FIFO is full.                                                                                                              |

| Q8-Q0        | 0   | Data Outputs                         | Data are read from the FIFO memory on these outputs.                                                                                                                                                                                                                                                |

| WEN2/<br>LD  | i   | Write Enable 2/<br>Register Load     | If WEN2/LD is LOW during the reset operation, this signal will subsequently function as an LD pin to control offset register load and read operations. If WEN2/LD is HIGH during the reset operation, this signal will function as WEN2, a second active HIGH write enable pin.                     |

| WCLK         | 1   | Write Clock                          | Data are written into the FIFO on the rising edge of WCLK if WEN1 and WEN2 are asserted. The FF and PAF transitions are synchronized to the WCLK.                                                                                                                                                   |

| WEN1         | 1   | Write Enable 1                       | When WEN1 is LOW and WEN2 is HIGH on the rising edge of WCLK, data will be written into the FIFO.                                                                                                                                                                                                   |

| RS           | 1   | Reset                                | When $\overline{\text{RS}}$ is LOW the read and write pointers are set to the first location and all offset registers are reset to the default value. The output register is also initialized to zero. After the device is powered up, a reset is required before a write operation can take place. |

| Vcc          |     |                                      | +5V Power Supply                                                                                                                                                                                                                                                                                    |

| GND          |     |                                      | Ground at 0V                                                                                                                                                                                                                                                                                        |

### FUNCTIONAL DESCRIPTION

# Reset (RS)

A reset is initiated by bringing RS LOW. A reset is required after power-up before a write operation can take place.

During reset, the following occurs:

- 1) The internal read and write pointers are set to the first physical location.

- 2) The output register is initialized to zero.

- 3) The offset registers are initialized to their default values

- 4) The Empty flag (EF) and Programmable Almost-Empty flag (PAE) will reset to LOW.

- 5) The Full flag (FF) and Programmable Almost-Full flag (PAF) will reset to HIGH.

- 6) WEN2/LD signal is configured during reset.

# Read Enables (REN1), (REN2)

New data are read from the FIFO when REN1 and REN2 are both LOW during the rising edge of RCLK. If either read enable is HIGH, then the outputs will retain the previous data. When the FIFO is empty, then the read enable signals are ignored.

### Read Clock (RCLK)

When the read enable pins are both LOW, new data can be read from the FIFO on the LOW-to-HIGH transition of the read clock (RCLK). The Empty flag (EF) and Programmable Almost-Empty flag (PAE) are synchronized to the rising edge of the read clock (RCLK).

### Output Enable (OE)

When output enable  $(\overline{OE})$  is LOW, the parallel output buffers receive data from the output register independent of other input signals. The output data bus will go to a high-impedance state when the output enable  $(\overline{OE})$  goes HIGH. The flag outputs are not affected by output enable  $(\overline{OE})$ .

# Data-In (D8-D0)

Nine-bit-wide data bus input for writing the FIFO array.

### Write Enable 1 (WEN1)

When the FIFO is configured with the ability to program the offset registers then WEN1 is the only write enable signal. In this mode, when WEN1 is LOW on the rising edge of the write clock, then data are written into the FIFO at the next sequential location. In this rhode, when WEN1 and LD are LOW on the rising edge of the write clock (WCLK), then data are written into a programmable offset register.

When the FIFO is configured to have two write enable pins, then data is written into the FIFO at the next sequential location when WEN1 is LOW and WEN2 is HIGH on the rising edge of the write clock (WCLK). When the FIFO is full, the WEN1 signal is ignored except for loading offsets.

# Write Clock (WCLK)

A write occurs on the LOW-to-HIGH transition of the write clock (WCLK) when writing is enabled. All setup and hold times are with respect to this transition. The Full flag (FF) and Programmable Almost-Full flag (PAF) are synchronized to the rising edge of the write clock (WCLK). The write and read clocks can be tied together and driven by one external clock input, or they can be supplied by separate asynchronous clock inputs.

# Write Enable 2 (WEN2)/Load (LD)

This signal can function as a second write enable (WEN2) or as an offset register load/read control pin (LD). If WEN2 /LD is HIGH during reset, then this signal functions as WEN2. If WEN2/LD is LOW during reset, then this signal functions as LD. When this pin is configured as a second write enable pin (WEN2), then a write occurs when WEN1 is LOW and WEN2 is HIGH on the rising edge of the write clock (WCLK).

When the FIFO is full then the WEN2 signal is ignored except for loading registers. Having a second write enable pin allows for depth expansion. To allow programming of the offset registers WEN2/LD must be configured as an LD pin. There are four 9-bit offset registers. two registers for controlling the Programmable Almost-Empty flag (PAE) and two registers for controlling the Programmable Almost-Full flag (PAF).

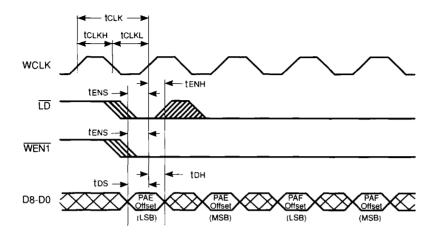

When LD and WEN1 are LOW, data are written to the least-significant bits, LSB almost-empty register on the first LOW-to-HIGH transition of the write clock. Data are written into the most significant bits, MSB, almost-empty register on the next LOW-to-HIGH transition of the write clock, and into the LSB almost-full register on the next transition and into the MSB almost-full register on the next transition. If more WCLK transitions occurred, the sequence would wrap around through the same sequence. When programming of the offset registers is interrupted, then the next register in sequence will be accessed when programming is resumed. In a similar fashion, the offset registers are read when both read enables REN1, REN2 and LD are LOW on the LOW-to-HIGH transition of the read clock (RCLK). The offset register sequence is the same as stated for programming the registers. Simultaneous write and read operations to the offset registers are not allowed.

# Output Data (Q8-Q0)

Memory array data and programmable offsets are read from these nine outputs.

# Empty Flag (EF)

When the read and write pointer are at the same location in the FIFO array, signifying that the FIFO is empty, the Empty flag (EF) goes LOW. The Empty flag is synchronized to the rising edge of the read clock (RCLK).

# Full Flag (FF)

When the Full flag (FF) goes LOW, then further write operations are inhibited. The Full flag is synchronized to the rising edge of the write clock (WCLK).

Programmable Almost-Empty Flag (PAE)

The Programmable Almost-Empty flag (PAE) is LOW after a reset pulse and will go HIGH when the write pointer is N+1 locations ahead of the read pointer where N is the value in the empty offset register. The default value for N is 7. The Programmable Almost-Empty flag (PAE) is synchronized to the rising edge of the read clock (RCLK).

# Programmable Almost-Full Flag (PAF)

The Programmable Almost-Full flag (PAF) goes LOW on the subsequent LOW-to-HIGH transition of the write clock (WCLK) when the write pointer becomes (FULL-N) locations ahead of the read pointer, where N is the value in the full offset register. The default value for N is 7.

**TABLE 2. WRITE OFFSET REGISTER**

| Operation        | WEN1 | WCLK     | ĹĎ |

|------------------|------|----------|----|

| No Operation     | 1    | <b>1</b> | 1  |

| Write in FIFO    | 0    | 1        | 1  |

| No Operation     | 1    | 1        | 0  |

| Empty Offset LSB | 0    | 1        | 0  |

| Empty Offset MSB | 0    | 1        | 0  |

| Full Offset LSB  | 0    | 1        | 0  |

| Full Offset MSB  | 0_   | 1        | 0  |

# Note:

The same sequence applies for reading the offset registers.

TABLE 3. LOCATION OF DATA IN OFFSET REGISTERS

| QS72211 512 x 9 BIT Synchronous FIFO Registers |   |   |   |   |   |   |   |   |   |

|------------------------------------------------|---|---|---|---|---|---|---|---|---|

| Data Inputs                                    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Empty LSB Offset                               | Х | • | • | • | • | • | • | • | L |

| Empty MSB Offset                               | Х | Х | Х | Х | Х | X | Х | Х | М |

| Full LSB Offset                                | Х | • |   | • | • | • | • | • | L |

| Full MSB Offset                                | Х | Х | Х | Х | Х | Х | Х | Х | М |

| QS72221 1K x 9 BIT Synchronous FIFO Registers |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------|---|---|---|---|---|---|---|---|---|

| Data Inputs                                   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Empty LSB Offset                              | Х | • | • | • | • | • | • | • | L |

| Empty MSB Offset                              | Х | Х | Х | Х | Х | Х | Х | М | • |

| Full LSB Offset                               | Х | • | • | • | • | • | • | • | L |

| Full MSB Offset                               | Х | Х | Χ | Х | Х | Х | Х | М | • |

| QS72231 2K x 9 BIT Synchronous FIFO Registers |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------|---|---|---|---|---|---|---|---|---|

| Data Inputs                                   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Empty LSB Offset                              | Х | • | • | • | • | • | • | • | L |

| Empty MSB Offset                              | Х | Х | Х | Х | Х | Х | М | • | • |

| Full LSB Offset                               | Х | • | • |   | • | • | • | • | L |

| Full MSB Offset                               | X | Х | Х | Х | Х | X | М |   | • |

| QS72241 4K x 9 BIT Synchronous FIFO Registers |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------|---|---|---|---|---|---|---|---|---|

| Data Inputs                                   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Empty LSB Offset                              | Χ | • | • | • | • | • | • | • | L |

| Empty MSB Offset                              | X | Х | Х | Х | Х | М | ٠ | • |   |

| Full LSB Offset                               | X | • | • | • | • | • | • | • | L |

| Full MSB Offset                               | Х | Х | Х | Х | Х | М | • |   | • |

- 1. L signifies LSB of data in offset registers.

- 2. M signifies MSB of data in offset registers.

- 3. X signifies do not care bit in offset registers.

- 4. The default value for both registers is 0007H.

**TABLE 4. STATUS OF FIFO FLAGS**

| Q\$72211                     | Q\$72221                      | EF | PAE | PAF | FF |

|------------------------------|-------------------------------|----|-----|-----|----|

| 0                            | 0                             | L  | L   | Н   | H  |

| 1 to I                       | 1 to I                        | Н  | L   | Н   | Н  |

| (I + 1) to $(512 - (J + 1))$ | (I + 1) to $(1024 - (J + 1))$ | Н  | Н   | Н   | Н  |

| (512 – J) to 511             | (1024 – J) to 1023            | Н  | Н   | L   | Н  |

| 512                          | 1024                          | Н  | Н   | L   | L  |

| QS72231                     | QS72241                     | EF | PAE | PAF | 풰 |

|-----------------------------|-----------------------------|----|-----|-----|---|

| 0                           | 0                           | L  | L   | Н   | Η |

| 1 to l                      | 1 to I                      | Н  | L   | Н   | Н |

| (I + 1) to (2048 – (J + 1)) | (I + 1) to (4096 – (J + 1)) | Н  | Н   | Н   | Н |

| (2048 – J) to 2047          | (4096 - J) to 4095          | Н  | Н   | L   | Н |

| 2048                        | 4096                        | Н  | Η   | L   | L |

#### Note:

I is the value in the empty offset register, and J is the value in the full offset register. The default value for I and J is 7.

**TABLE 5. POWER SUPPLY CHARACTERISTICS**

| Parameter          | Description          | Test Conditions           | 722X1-12 | 722X1-15 | 722X1-20 | Units |

|--------------------|----------------------|---------------------------|----------|----------|----------|-------|

| lcc <sup>(1)</sup> | Operating<br>Current | Vcc = Max,<br>lout = 0 mA | 150      | 125      | 100      | mA    |

| SB <sup>(2)</sup>  | Standby<br>Current   | Vcc = Max,<br>lout = 0 mA | 5        | 5        | 5        | mA    |

| Parameter          | Description          | Test Conditions           | 722X1-25 | 722X1-35 | 722X1-50 | Units |

|--------------------|----------------------|---------------------------|----------|----------|----------|-------|

| lcc <sup>(1)</sup> | Operating<br>Current | Vcc ≈ Max.<br>lout ≈ 0 mA | 80       | 45       | 40       | mA    |

| ÍsB <sup>(2)</sup> | Standby<br>Current   | Vcc ≈ Max,<br>lout ≈ 0 mA | 5        | 5        | 5        | mA    |

- 1. Input signals switch from 0V to 3V with a rise/fall time of less than 3ns, clocks and clock enables switch at maximum frequency (fмax), while data inputs switch at fмax/2. Outputs are unloaded.

- 2. All input signals are connected to Vcc. All outputs are unloaded. Read and write clocks switch at maximum frequency (fmax).

### TABLE 6. ABSOLUTE MAXIMUM RATINGS

| Supply Voltage to Ground                | 0.5V to +7.0V  |

|-----------------------------------------|----------------|

| DC Input Voltage VIN                    | 0.5V to 7.0V   |

| AC Input Voltage (Pulse Width 20 ns)    | 5.0V           |

| DC Output Current Max. Sink Current/Pin | 50 mA          |

| Tstg Storage Temperature                | 55°C to +125°C |

Note: Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to this device resulting in functional or reliability type failures.

# TABLE 7. CAPACITANCE

$T_A = 25^{\circ}C$ , f = 1.0 MHz

| Name | Description(1)        | Conditions | Тур | Max | Units |

|------|-----------------------|------------|-----|-----|-------|

| Cin  | Input Capacitance     | Vin = 0V   | _   | 10  | рF    |

| Соит | Output Capacitance(2) | Vout = 0V  | -   | 10  | pF    |

### Notes:

- 1. Capacitance is guaranteed but not tested.

- 2. Outputs are deselected, OE is HIGH.

# TABLE 8. DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$

| Symbol | Parameter           | Test Conditions                        | Min | Max | Units |

|--------|---------------------|----------------------------------------|-----|-----|-------|

| Vін    | Input HIGH Voltage  | Logic HIGH for All Inputs              | 2.0 | _   | V     |

| VIL    | Input LOW Voltage   | Logic LOW for All Inputs               |     | 0.8 | ٧     |

| Vон    | Output HIGH Voltage | lон = −2 mA                            | 2.4 | _   | ٧     |

| Vol    | Output LOW Voltage  | lot = 8 mA                             | _   | 0.4 | V     |

| loz    | Output Leakage      | Vcc = Max, Vin = GND to Vcc<br>OE V in | -10 | +10 | μА    |

| fı∟    | Input Leakage       | Vcc = 5.5V, Vin = GND to Vcc           | -1  | +1  | μA    |

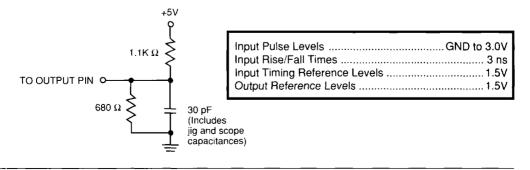

# FIGURE 3. AC TEST CONDITIONS

# **TABLE 9. AC ELECTRICAL CHARACTERISTICS**

$T_A = 0$ °C to 70°C,  $V_{CC} = 5V \pm 10$ %

|             |                                                                                    |     | Speed (ns)  |     |          |     |                |       |

|-------------|------------------------------------------------------------------------------------|-----|-------------|-----|----------|-----|----------------|-------|

|             |                                                                                    |     | -12 -15 -20 |     |          | 20  |                |       |

| Symbol      | Parameter                                                                          | Min | Max         | Min | Max      | Min | Max            | Units |

| fs          | Clock Cycle Frequency .                                                            |     | 83          | _   | 66.7     | _   | 50             | MHz   |

| tA          | Data Access Time                                                                   | 2   | 9           | 2   | 10       | 2   | 12             | ns    |

| tclk        | Clock Cycle Time                                                                   | 12  | _           | 15  | _        | 20  | [ <del>-</del> | ns    |

| tclkh       | Clock HIGH Time                                                                    | 5   | _           | 6   | _        | 8   | _              | ns    |

| tclkl       | Clock LOW Time                                                                     | 5   |             | 6   |          | 8   | _              | ns    |

| tos         | Data Setup Time                                                                    | 3   | _           | 4   | _        | 5   | _              | ns    |

| tон         | Data Hold Time                                                                     | 1   | _           | 1   | =        | 1   | _              | ns    |

| tens        | Enable Setup Time                                                                  | 3   | _           | 4   | _        | 5   | _              | ns    |

| tenn        | Enable Hold Time                                                                   | 1   |             | 1   |          | 1   | _              | ns    |

| trs         | Reset Pulse Width(1)                                                               | 12  |             | 15  | <u> </u> | 20  | _              | ns    |

| tass        | Reset Setup Time                                                                   | 12  | _           | 15  | <u> </u> | 20  |                | ns    |

| trsf        | Reset to Flag and Output Valid                                                     |     | 12          |     | 15       | _   | 20             | ns    |

| <b>t</b> oE | Output Enable to Output Valid                                                      | 3   | 7           | 3   | 8        | 3   | 10             | ns    |

| torz        | Output Enable to Output LOW(2)                                                     | 0   | _           | 0   | _        | 0   |                | ns    |

| tonz        | Output Enable to Output HIGH(2)                                                    | 3   | 7           | 3   | 8        | 3   | 10             | ns    |

| twff        | Write Clock to Full Flag                                                           |     | 9           |     | 10       |     | 12             | ns    |

| TREF        | Read Clock to Empty Flag                                                           |     | 9           | Ī-  | 10       | _   | 12             | ns    |

| tpaf        | Write Clock to Programmable<br>Almost-Full Flag                                    |     | 9           | _   | 10       | _   | 12             | ns    |

| tpae        | Read Clock to Programmable<br>Almost-Empty Flag                                    | _   | 9           | -   | 10       | -   | 12             | ns    |

| tskew1      | Skew Time between Read Clock and Write Clock for Empty Flag and Full Flag          | 5   | _           | 6   | -        | 8   | -              | ns    |

| tskew2      | Skew Time between Read Clock and Write Clock for Almost-Empty and Almost-Full Flag | 22  | _           | 28  | _        | 35  | !              | ns    |

Notes: 1. Pulse widths less than minimum values are not allowed.

<sup>2.</sup> Values are generated by design, not currently tested.

# TABLE 9. AC ELECTRICAL CHARACTERISTICS

$T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$

|             |                                                                                    |          | Speed (ns) |     |      |     |     |       |

|-------------|------------------------------------------------------------------------------------|----------|------------|-----|------|-----|-----|-------|

|             |                                                                                    |          | -25 -35`   |     |      | -50 |     |       |

| Symbol      | Parameter                                                                          | Min      | Max        | Min | Max  | Min | Max | Units |

| fs          | Clock Cycle Frequency                                                              |          | 40         | _   | 28.6 | _   | 20  | MHz   |

| tA          | Data Access Time                                                                   | 2        | 15         | 2   | 20   |     | 25  | ns    |

| tclk        | Clock Cycle Time                                                                   | 25       | _          | 35  | _    | 50  | _   | ns    |

| tclkH       | Clock HIGH Time                                                                    | 10       |            | 14  | _    | 20  | _   | ns    |

| tclkl       | Clock LOW Time                                                                     | 10       | _          | 14  |      | 20  |     | ns    |

| tos         | Data Setup Time                                                                    | 6        | _          | 8   | -    | 10  | [-  | ns    |

| tDH         | Data Hold Time                                                                     | 1        |            | 2   |      | 2   | _   | ns    |

| tens        | Enable Setup Time                                                                  | 6        |            | 8   | _    | 10  | _   | ns    |

| tenn        | Enable Hold Time                                                                   | 1        | _          | 2   | -    | 2   |     | ns    |

| tas         | Reset Pulse Width <sup>(1)</sup>                                                   | 25       |            | 35  |      | 50  | _   | ns    |

| trss        | Reset Setup Time                                                                   | 25       |            | 35  |      | 50  | _   | ns    |

| trsr        | Reset to Flag and Output Valid                                                     |          | 25         |     | 35   |     | 50  | ns    |

| toe         | Output Enable to Output Valid                                                      | 3        | 13         | 3   | 15   | 3   | 25  | ns    |

| toLZ        | Output Enable to Output LOW(2)                                                     | 0        |            | 0   | _    | 0   | _   | ns    |

| tonz        | Output Enable to Output HIGH(2)                                                    | 3        | 13         | 3   | 15   | 3   | 25  | ns    |

| twff        | Write Clock to Full Flag                                                           | <u> </u> | 15         | _   | 20   | _   | 30  | ns    |

| tref        | Read Clock to Empty Flag                                                           |          | 15         | _   | 20   | _   | 30  | ns    |

| <b>TPAF</b> | Write Clock to Programmable<br>Almost-Full Flag                                    |          | 15         |     | 20   | _   | 30  | ns    |

| tpae        | Read Clock to Programmable<br>Almost-Empty Flag                                    |          | 15         | _   | 20   | _   | 30  | ns    |

| tskew1      | Skew Time between<br>Read Clock and Write Clock<br>for Empty Flag and Full Flag    | 10       | _          | 12  | _    | 15  |     | ns    |

| tskew2      | Skew Time between Read Clock and Write Clock for Almost-Empty and Almost-Full Flag | 40       | _          | 42  |      | 45  |     | ns    |

Notes: 1. Pulse widths less than minimum values are not allowed.

<sup>2.</sup> Values are generated by design, not currently tested.

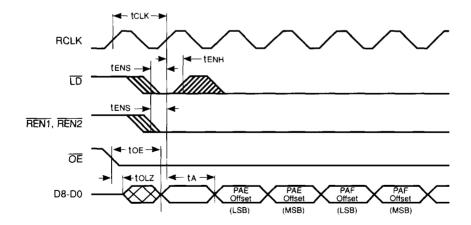

# **TIMING DIAGRAMS**

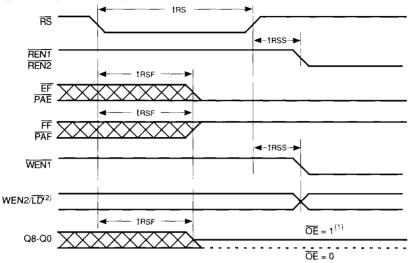

# FIGURE 4. RESET TIMING

- After reset, the outputs will be low if OE = 0 and three-state if OE = 1.

If WEN2/LD is LOW during a reset, then it will be configured as a LD pin.

If WEN2/LD is HIGH during a reset, then it will be configured as a WEN2 pin.

The clock (RCLK, WCLK) can be free-running during reset.

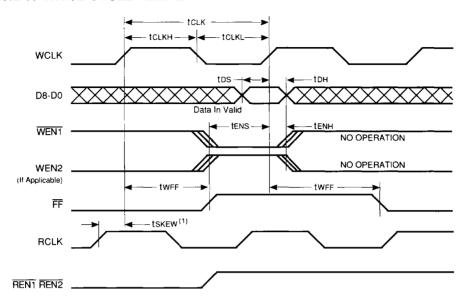

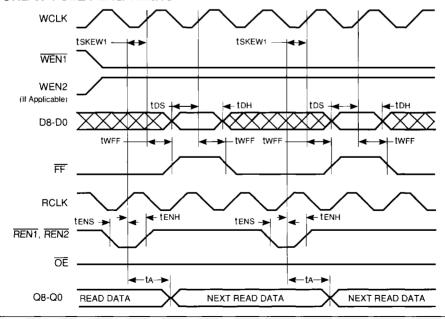

# FIGURE 5. WRITE CYCLE TIMING

### Notes:

1. tskew 1 is the minimum time between the rising edge of RCLK and the rising edge of WCLK for an FF transition to occur in that clock cycle. If the tskew1 is not satisfied, then an FF transition may not occur until the next WCLK edge.

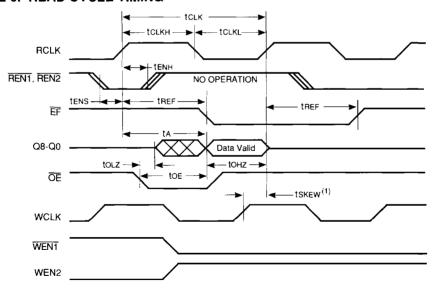

# FIGURE 6. READ CYCLE TIMING

#### Notes:

1. tskew 1 is the minimum time between the rising edge of WCLK and the rising edge of RCLK for an EF transition to occur in that clock cycle. If the tskew1 is not satisfied, then an EF transition may not occur until the next RCLK edge.

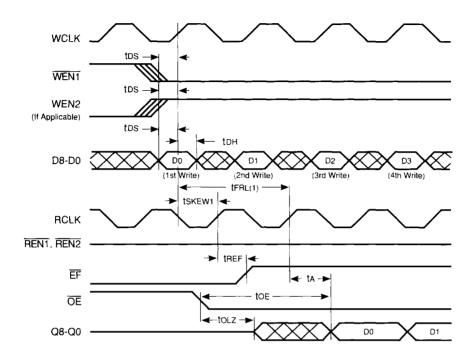

FIGURE 7. FIRST DATA WORD LATENCY TIMING

#### Notes:

1. The latency timing is only relevant when the Empty flag is LOW.

When tskew1 is greater than minimum specifications, tfrl = tclk + tskew1.

When tskew1 is less than minimum specifications, tfrl = 2(tclk) + tskew1.

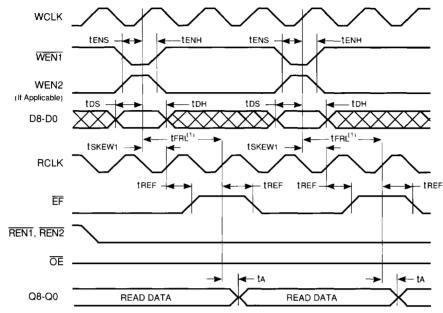

# FIGURE 8. EMPTY FLAG TIMING

#### Notes:

The latency timing is only relevant when the Empty flag is LOW.

When tskew1 is greater than minimum specifications, tfrl = tclk + tskew1.

When tskew1 is less than minimum specifications, tfrl = 2(tclk) + tskew1.

# FIGURE 9. FULL FLAG TIMING

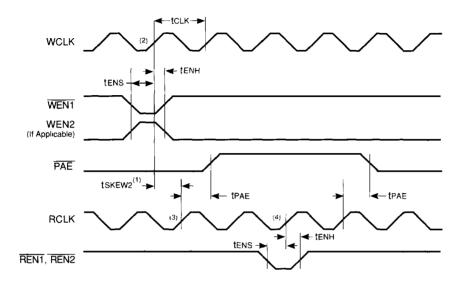

# FIGURE 10. PROGRAMMABLE ALMOST-EMPTY FLAG TIMING

- 1. tskew2 is the minimum time between the rising edge of WCLK and the rising edge of RCLK to guarantee that PAE will make a transition to HIGH during that clock cycle. If tskew2 timing is not met, then PAE may not make a transition to HIGH until the next rising edge of RCLK.

- 2. This write cycle is (N+1) locations ahead of the read pointer. N is the value in the programmable Almost-Empty flag register.

- 3. PAE is synchronized to the rising edge of RCLK.

- 4. PAE is synchronized to the rising edge of RCLK, but the PAE transition takes place in the next clock cycle.

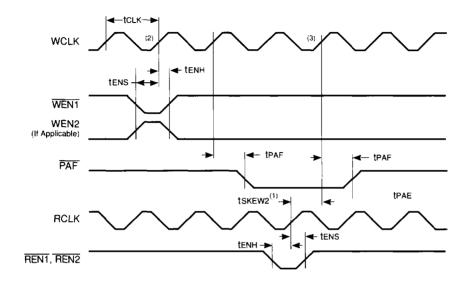

FIGURE 11. PROGRAMMABLE ALMOST-FULL FLAG TIMING

- 1 tskew2 is the minimum time between the rising edge of RCLK and the rising edge of WCLK to guarantee that PAE will make a transition to HIGH during that clock cycle. If tskew2 timing is not met, then PAE may not make a transition to HIGH until the next rising edge of WCLK.

- 2 This write cycle is FULL-N locations ahead of the read pointer. N is the value in the programmable Almost-Full flag register.

- 3. PAF is synchronized to the rising edge of WCLK.

- 4. PAF is synchronized to the rising edge of WCLK, but the PAF transition takes place in the next clock cycle.

# FIGURE 12. WRITE OFFSET REGISTER TIMING

FIGURE 13. READ OFFSET REGISTER TIMING

# **OPERATING MODES**

# Single-Device Mode

A single QS72211/221/231/241 may be used when the user requirements are for 512, 1K, 2K or 4K words, respectively. Figure 15 depicts the FIFO in this mcde. Read enable 2 ( $\overline{REN2}$ ) is grounded and WEN2/ $\overline{LD}$  is LOW during reset, so this signal functions as a register load pin ( $\overline{LD}$ ).

### Depth-Expansion Mode

The second write enable (WEN2) is for applications requiring depth expansion. WEN2/LD is HIGH during reset, so the signal functions as a WEN2. External logic is then used to direct the flow of data into the cascaded FIFOs.

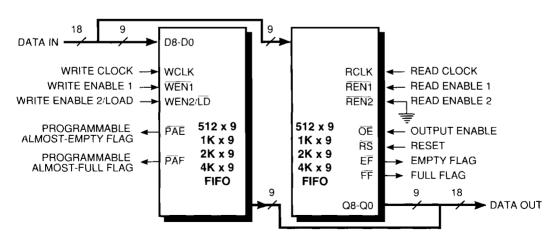

# Width-Expansion Mode

The width of the data word can be increased by connecting corresponding input control signals to multiple FIFOs. Figure 16 shows an 18-bit word width using two QS72V2X1 devices. The word width can be increased by using additional FIFOs. In the example, read enable 2 ( $\overline{REN2}$ ) is grounded and WEN2/ $\overline{LD}$  is LOW during reset. so the signal functions as a register load pin ( $\overline{LD}$ ). The status of the flags can be had from any one of the FIFOs.

# FIGURE 15. SINGLE-DEVICE MODE

### FIGURE 16. WIDTH-EXPANSION MODE

# **ORDERING INFORMATION**

# Example: