# M.2 2280 PCIe SSD 920 Datasheet (SQF-CM8xx-xG-ECx)

## CONTENTS

| Safety Instructions               |    |

|-----------------------------------|----|

| Consignes de sécurité             | 4  |

| 1. Overview                       | 5  |

| 2. Features                       | 6  |

| 3. Specification Table            | 7  |

| 4. General Description            |    |

| 5. Security Features              |    |

| 6. Pin Assignment and Description | 13 |

| 7. NVMe Command List              | 15 |

| 8. Identify Device Data           |    |

| 9. System Power Consumption       |    |

| 10. Physical Dimension            |    |

| Appendix: Part Number Table       |    |

| ••                                |    |

#### **Revision History**

| Rev. | Date      | History                                     |

|------|-----------|---------------------------------------------|

| 0.1  | 2018/5/18 | 1. Preliminary release                      |

| 0.2  | 2018/8/18 | 1. Update PN information                    |

| 0.3  | 2018/9/18 | 1. Update Physical Dimension (draft)        |

| 0.4  | 2019/1/23 | 1. Update performance & related information |

| 0.5  | 2019/1/23 | 1. Update performance information           |

| 0.6  | 2019/3/5  | 1. Update sustained performance             |

| 0.7  | 2019/3/12 | 1. Update power consumption & performance   |

| 0.8  | 2019/4/12 | 1. Performance update                       |

| 0.9  | 2019/5/5  | 1. Modify description                       |

| 1.0  | 2019/7/1  | 1. Added function support information       |

| 1.1  | 2019/7/19 | 1. Added security description               |

| 1.2  | 2019/7/23 | 1. Performance update                       |

| 1.3  | 2020/1/9  | 1. Updated Pin Assignment and Description   |

| 1.4  | 2020/2/11 | 1. Calibration product dimension            |

| 1.5  | 2020/4/9  | 1. Added power consumption information      |

| 1.6  | 2020/6/10 | 1. Added certification information.         |

| 1.7  | 2020/6/22 | 1. Added TBW data                           |

|      |           |                                             |

Advantech reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Advantech is believed to be accurate and reliable. However, Advantech does not assure any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. Copyright © 1983-2020 Advantech Co., Ltd. All rights reserved.

#### Safety Instructions

- 1. Read these safety instructions carefully.

- 2. Keep this User Manual for later reference.

- 3. Disconnect this equipment from any AC outlet before cleaning. Use a damp cloth. Do not use liquid or spray detergents for cleaning.

- 4. For plug-in equipment, the power outlet socket must be located near the equipment and must be easily accessible.

- 5. Keep this equipment away from humidity.

- 6. Put this equipment on a reliable surface during installation. Dropping it or letting it fall may cause damage.

- 7. The openings on the enclosure are for air convection. Protect the equipment from overheating. DO NOT COVER THE OPENINGS.

- 8. Make sure the voltage of the power source is correct before connecting the equipment to the power outlet.

- 9. Position the power cord so that people cannot step on it. Do not place anything over the power cord.

- 10. All cautions and warnings on the equipment should be noted.

- 11. If the equipment is not used for a long time, disconnect it from the power source to avoid damage by transient overvoltage.

- 12. Never pour any liquid into an opening. This may cause fire or electrical shock.

- 13. Never open the equipment. For safety reasons, the equipment should be opened only by qualified service personnel.

- 14. If one of the following situations arises, get the equipment checked by service personnel:

- The power cord or plug is damaged.

- Liquid has penetrated the equipment.

- The equipment has been exposed to moisture.

- The equipment does not work well, or you cannot get it to work according to the user's manual.

- The equipment has been dropped and damaged.

- The equipment has obvious signs of breakage.

- 15. DO NOT LEAVE THIS EQUIPMENT IN AN ENVIRONMENT WHERE THE STORAGE TEMPERATURE MAY GO BELOW -20° C (-4° F) OR ABOVE 60° C (140° F). THIS COULD DAMAGE THE EQUIPMENT. THE EQUIPMENT SHOULD BE IN A CONTROLLED ENVIRONMENT.

- 16. CAUTION: DANGER OF EXPLOSION IF BATTERY IS INCORRECTLY REPLACED. REPLACE ONLY WITH THE SAME OR EQUIVALENT TYPE RECOMMENDED BY THE MANUFACTURER, DISCARD USED BATTERIES ACCORDING TO THE MANUFACTURER'S INSTRUCTIONS.

#### Consignes de sécurité

- 1. Lisez attentivement ces instructions de sécurité.

- 2. Conservez ce manuel pour référence ultérieure.

- 3. Débranchez cet appareil de toute prise secteur avant le nettoyage. Utilisez un chiffon humide. Ne pas utiliser de détergents liquides ou en aérosol pour le nettoyage

- 4. Pour les équipements enfichables, la prise de courant doit être située près de l'équipement et doit être facilement accessible.

- 5. Gardez cet équipement à l'abri de l'humidité.

- 6. Placez cet équipement sur une surface fiable lors de l'installation. Le laisser tomber ou le laisser tomber peut causer des dommages.

- Les ouvertures sur l'enceinte sont destinées à la convection de l'air. Protégez l'équipement de la surchauffe. NE COUVREZ PAS LES OUVERTURES.

- 8. Assurez-vous que la tension de la source d'alimentation est correcte avant de connecter l'équipement à la prise de courant.

- 9. Positionnez le cordon d'alimentation de sorte que personne ne puisse marcher dessus. Ne placez rien sur le cordon d'alimentation.

- 10. Toutes les mises en garde et avertissements sur l'équipement doivent être notés..

- 11. Si l'appareil n'est pas utilisé pendant une longue période, débranchez-le de la source d'alimentation pour éviter tout dommage dû à une surtension transitoire.

- 12. Ne jamais verser de liquide dans une ouverture. Cela pourrait provoquer un incendie ou un choc électrique.

- 13. N'ouvrez jamais l'équipement. Pour des raisons de sécurité, l'équipement ne doit être ouvert que par du personnel qualifié.

- 14. Si l'une des situations suivantes se produit, faites vérifier l'équipement par le personnel de service:l:

- Le cordon d'alimentation ou la fiche est endommagé Liquid has penetrated the equipment.

- L'équipement a été exposé à l'humidité.

- L'équipement ne fonctionne pas bien ou vous ne pouvez pas le faire fonctionner conformément au manuel d'utilisation..

- L'équipement est tombé et endommagé..

- L'équipement présente des signes évidents de rupture.

- 15. NE PAS LAISSER CET APPAREIL DANS UN ENVIRONNEMENT O LA TEMPÉRATURE DE STOCKAGE PEUT ÊTRE INFÉRIEURE À -20 ° C (-4 ° F) OU SUPÉRIEURE À 60 ° C (140 ° F). CELA POURRAIT ENDOMMAGER L'ÉQUIPEMENT. L'ÉQUIPEMENT DOIT ÊTRE DANS UN ENVIRONNEMENT CONTRÔLÉ.

- 16. ATTENTION: DANGER D'EXPLOSION EN CAS DE REMPLACEMENT INCORRECT DE LA PILE. REMPLACEZ UNIQUEMENT AVEC LE MÊME TYPE OU LE TYPE ÉQUIVALENT RECOMMANDÉ PAR LE FABRICANT, DÉJETTEZ LES PILES UTILISÉES SELON LES INSTRUCTIONS DU FABRICANT.

## 1. <u>Overview</u>

Advantech SQFlash 920 series M.2 2280 PCIe SSD (Solid State Drive) delivers all the advantages of flash disk technology with PCIe Gen3 x4 interface, including being compliant with standard M.2 2280 (M Key) form factor. The device is designed to operate at a maximum operating frequency of 200MHz with 25MHz external crystal. Its capacity could provide a wide range up to 1.9TB. Moreover, it can reach up to 3,400MB/s read as well as 2,700MB/s write high performance based on Toshiba 64-layer 3D TLC Flash.

## 2. <u>Features</u>

## PCIe Interface

- Compliant with NVMe1.3

- Compatible with PCIe I/II/III x4 interface

- Support up to queue depth 64K

**ADVANTECH**

- Support power management

- Operating Voltage : 3.3V

- Support LDPC with RAID ECC

- AES256 、TCG-OPAL 、TRIM 、AHCI supported

- Hardware Quick Erase supported (optional)

- Voltage Stabilizer supported (optional)

## Temperature Ranges<sup>1</sup>

- Commercial Temperature

- 0°C to 70°C for operating

- -40°C to 85°C for storage

- Industrial Temperature

- -40  $^\circ\!\mathrm{C}$  to 85  $^\circ\!\mathrm{C}$  for operating

- -40°C to 85°C for storage

\*Note : 1. Based on SMART Attribute (Byte index [2 :1] of PCIe-SIG standard, which measured by thermal sensor

## Mechanical Specification

- Shock : 1,500G / 0.5ms

- Vibration : 20G / 80~2,000Hz

- Humidty

- Humidity : 5% ~ 95% under 55°C

- Acquired RoHS、WHQL、CE、FCC Certificate

- Acoustic : 0 dB

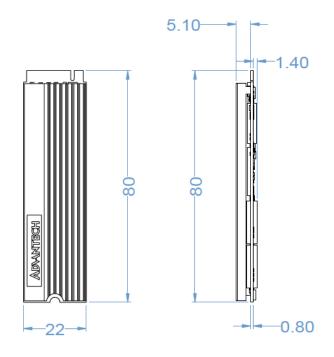

- Dimension : 80.0 mm x 22.0 mm x 7.3 mm

## 3. Specification Table

#### Performance

|         |         | Sequential (MB/sec) |       | Random ( | IOPS @4K) |

|---------|---------|---------------------|-------|----------|-----------|

|         |         | Read                | Write | Read     | Write     |

|         | 240 GB  | 3000                | 1000  | 160K     | 237K      |

| 3D TLC  | 480 GB  | 3400                | 2100  | 357K     | 445K      |

| (BiCS3) | 960 GB  | 3400                | 2700  | 350K     | 230K      |

|         | 1920 GB | 3400                | 2700  | 360K     | 199K      |

\* Performance measured by IOMeter with QD32, 8GB data pattern, SLC pool enable & adjustable by request.

#### Endurance

JEDEC defined an endurance rating TBW (TeraByte Written), following by the equation below, for indicating the number of terabytes a SSD can be written which is a measurement of SSDs' expected lifespan, represents the amount of data written to the device.

#### TBW = [(NAND Endurance) x (SSD Capacity)] / WAF

- NAND Endurance: Program / Erase cycle of a NAND flash.

- SLC: 100,000 cycles

- Ultra MLC: 30,000 cycles

- o MLC: 3,000 cycles

- o 3D TLC (BiCS3): 3,000 cycles

- SSD Capacity: SSD physical capacity in total of a SSD.

- **WAF**: Write Amplification Factor (WAF), as the equation shown below, is a numerical value representing the ratio between the amount of data that a SSD controller needs to write and the amount of data that the host's flash controller writes. A better WAF, which is near to 1, guarantees better endurance and lower frequency of data written to flash memory.

#### WAF = (Lifetime write to flash) / (Lifetime write to host)

- Endurance measurement is based on New JEDEC 219 Client Workload and verified with following workload conditions,

- PreCond%full = 100%

- Trim commands enabled

- Random data pattern.

| 3D TLC<br>(BiCS3) | WAF  | TBW  | DWPD* |

|-------------------|------|------|-------|

| 240 GB            | 2.0  | 380  | 1.45  |

| 480 GB            | 1.81 | 850  | 1.62  |

| 960 GB            | 1.85 | 1665 | 1.58  |

| 1920 GB           | 1.97 | 3115 | 1.48  |

\* Endurance of 1 drive writes per day (DWPD) for 3 years

- Pure sequential workload conditions, fio seq write, 30 loops, bs 128k, io depth 32 (Copy the pattern by VDbench)

| 3D TLC<br>(BiCS3) | WAF  | TBW  | DWPD* |

|-------------------|------|------|-------|

| 240 GB            | 1.05 | 714  | 2.74  |

| 480 GB            | 1.05 | 1429 | 2.72  |

| 960 GB            | 1.05 | 2857 | 2.72  |

| 1920 GB           | 1.05 | 5714 | 2.72  |

\* Endurance of 1 drive writes per day (DWPD) for 3 years

## 4. General Description

#### Error Correction Code (ECC)

Flash memory cells will deteriorate with use, which might generate random bit errors in the stored data. Thus, SQFlash 920 series PCIe SSD applies the LDPC with RAID ECC algorithm, which can detect and correct errors occur during read process, ensure data been read correctly, as well as protect data from corruption.

#### Wear Leveling

NAND flash devices can only undergo a limited number of program/erase cycles, and in most cases, the flash media are not used evenly. If some areas get updated more frequently than others, the lifetime of the device would be reduced significantly. Thus, Wear Leveling is applied to extend the lifespan of NAND Flash by evenly distributing write and erase cycles across the media.

SQFlash provides advanced Wear Leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. Moreover, by implementing both dynamic and static Wear Leveling algorithms, the life expectancy of the NAND flash is greatly improved.

#### Bad Block Management

Bad blocks are blocks that include one or more invalid bits, and their reliability is not guaranteed. Blocks that are identified and marked as bad by the manufacturer are referred to as "Initial Bad Blocks". Bad blocks that are developed during the lifespan of the flash are named "Later Bad Blocks". SQFlash implements an efficient bad block management algorithm to detect the factory-produced bad blocks and manages any bad blocks that appear with use. This practice further prevents data being stored into bad blocks and improves the data reliability.

#### Power Loss Protection

#### Flush Manager

Power Loss Protection is a mechanism to prevent data loss during unexpected power failure. DRAM is a volatile memory and frequently used as temporary cache or buffer between the controller and the NAND flash to improve the SSD performance. However, one major concern of the DRAM is that it is not able to keep data during power failure. Accordingly, SQFlash SSD applies the Flush Manager technology, only when the data is fully committed to the NAND flash will the controller send acknowledgement (ACK) to the host. Such implementation can prevent false-positive performance and the risk of power cycling issues.

In addition, it is critical for a controller to shorten the time the in-flight data stays in the controller internal cache. Thus, SQFlash applies an algorithm to reduce the amount of data resides in the cache to provide a better performance. With Flush Manager, incoming data would only have a "pit stop" in the cache and then move to NAND flash directly. Also, the onboard DDR will be treated as an "organizer" to consolidate incoming data into groups before written into the flash to improve write amplification.

#### Voltage Stabilizer

While the built-in voltage detector detects an unstable power input (< 3.135 V or > 3.465 V), the controller will issue a power failure interrupt and force a Flush CMD first. At the same time, the whole internal power supply will be switched to Voltage Stabilizer immediately to ensure stable power is supplied throughout the whole drive. This ensures the Flash IC and DDR IC will not operate with unstable power which could lead to data errors or bad data integrity.

#### TRIM

TRIM is a feature which helps improve the read/write performance and speed of solid-state drives (SSD). Unlike hard disk drives (HDD), SSDs are not able to overwrite existing data, so the available space gradually becomes smaller with each use. With the TRIM command, the operating system can inform the SSD which blocks of data are no longer in use and can be removed permanently. Thus, the SSD will perform the erase action, which prevents unused data from occupying blocks all the time.

## **ADVANTECH**

#### SMART

SMART, an acronym for Self-Monitoring, Analysis and Reporting Technology, is an open standard that allows a hard disk drive to automatically detect its health and report potential failures. When a failure is recorded by SMART, users can choose to replace the drive to prevent unexpected outage or data loss. Moreover, SMART can inform users of impending failures while there is still time to perform proactive actions, such as copy data to another device.

#### Over-Provision

Over Provisioning refers to the inclusion of extra NAND capacity in a SSD, which is not visible and cannot be used by users. With Over Provisioning, the performance and IOPS (Input/Output Operations per Second) are improved by providing the controller additional space to manage P/E cycles, which enhances the reliability and endurance as well. Moreover, the write amplification of the SSD becomes lower when the controller writes data to the flash.

#### Thermal Throttling

Thermal Throttling function is for protecting the drive and reducing the possibility of read / write error due to overheat. The temperature is monitored by the thermal sensor. As the operating temperature continues to increase to threshold temperature, the Thermal Throttling mechanism is activated. At this time, the performance of the drive will be significantly decreased to avoid continuous heating. When the operating temperature falls below threshold temperature, the drive can resume to normal operation.

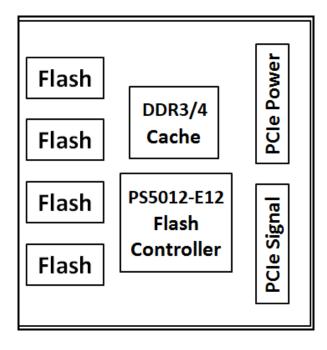

#### Block Diagram

#### LBA value

| Density (GB) | LBA           |

|--------------|---------------|

| 240          | 468,862,128   |

| 480          | 937,703,088   |

| 960          | 1,875,385,008 |

| 1920         | 3,750,748,848 |

## 5. <u>Security Features</u>

#### Advanced Encryption Standard (AES)

An AES 256-bit encryption key is generated in the drive's security controller before the data got stored on the NAND flash. When the controller or firmware fails, the data that is securely stored in the encryption key becomes inaccessible through the NAND flash.

#### **TCG-OPAL 2.0 Compliance**

TCG-OPAL compliance SED (Self-encryption Drive) supports a built-in shadow MBR to process user authentication to SSD before booting to normal MRR area and OS. SQFlash 920 series supports such feature with 100% TCG-OPAL compliance. Further, with SQFlash Flash Lock function, the user authentication process in shadow MBR can be done automatically by bonding with motherboard unique ID such as UUID in BIOS / MAC address / TPM unique code. So with Flash Lock enabled, only designated motherboard can have access to the SSD.

#### Flash Vault

Flash Vault is to lock Read and Write command by SSD firmware setting and make the SSD need password to verify and only operate with the corresponding platform. User can use Flash Vault to prevent data being stolen by reading the SQFlash SSD with other computers and unauthorized person.

#### Security ID

Security ID is to encrypt user's specific application software encryption. To enable this function, the application software is required to build Security ID function code and user needs to enable the firmware function by entering Access Code of SQFlash Utility, and then the Security ID can be set. When Security ID sets, the application software is protected by Security ID and SQFlash Utility

## 6. Pin Assignment and Description

| 1GNDGround23.3V3.3V source3GNDGround43.3V3.3V source5PETn3PCle TX Differential signal defined by the PCle 3.06N/CNo connect7PETp3PCle TX Differential signal defined by the PCle 3.0 spr8N/CNo connect9GNDGround10LED1#(O)Status indicators via LED devices11PERn3PCle RX Differential signal defined by the PCle 3.0 spr123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 spr143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 spr183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spr20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spr24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spr26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spr30N/CNo connect                                                                                                       | ecification  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3GNDGround43.3V3.3V source5PETn3PCle TX Differential signal defined by the PCle 3.06N/CNo connect7PETp3PCle TX Differential signal defined by the PCle 3.0 spr8N/CNo connect9GNDGround10LED1#(O)Status indicators via LED devices11PERn3PCle RX Differential signal defined by the PCle 3.0 spr123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 spr143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 spr183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spr20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spr24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spr26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spr                                                                                                                                                | ecification  |

| 3GNDGround43.3V3.3V source5PETn3PCle TX Differential signal defined by the PCle 3.06N/CNo connect7PETp3PCle TX Differential signal defined by the PCle 3.0 spr8N/CNo connect9GNDGround10LED1#(O)Status indicators via LED devices11PERp3PCle RX Differential signal defined by the PCle 3.0 spr123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 spr143.3V3.3V source15GNDGround163.3V3.3V source17PETp2PCle TX Differential signal defined by the PCle 3.0 spr183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spr20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spr24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spr26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spr                                                                                                                                                | ecification  |

| 5PETn3PCle TX Differential signal defined by the PCle 3.06N/CNo connect7PETp3PCle TX Differential signal defined by the PCle 3.0 spr8N/CNo connect9GNDGround10LED1#(O)Status indicators via LED devices11PERn3PCle RX Differential signal defined by the PCle 3.0 spr123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 spr143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 spr183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spr20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spr24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spr26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spr                                                                                                                                                                          | ecification  |

| 6     N/C     No connect       7     PETp3     PCIe TX Differential signal defined by the PCIe 3.0 sponder       8     N/C     No connect       9     GND     Ground       10     LED1#(O)     Status indicators via LED devices       11     PERn3     PCIe RX Differential signal defined by the PCIe 3.0 sponder       12     3.3V     3.3V source       13     PERp3     PCIe RX Differential signals defined by the PCIe 3.0 sponder       14     3.3V     3.3V source       15     GND     Ground       16     3.3V     3.3V source       17     PETn2     PCIe TX Differential signal defined by the PCIe 3.0 sponder       18     3.3V     3.3V source       19     PETp2     PCIe TX Differential signal defined by the PCIe 3.0 sponder       20     N/C     No connect       21     GND     Ground       22     N/C     No connect       23     PERn2     PCIe RX Differential signal defined by the PCIe 3.0 sponder       23     PERn2     PCIe RX Differential signal defined by the PCIe 3.0 sponder | ecification  |

| 6   N/C   No connect     7   PETp3   PCIe TX Differential signal defined by the PCIe 3.0 spression     8   N/C   No connect     9   GND   Ground     10   LED1#(O)   Status indicators via LED devices     11   PERn3   PCIe RX Differential signal defined by the PCIe 3.0 spression     12   3.3V   3.3V source     13   PERp3   PCIe RX Differential signals defined by the PCIe 3.0 spression     14   3.3V   3.3V source     15   GND   Ground     16   3.3V   3.3V source     17   PETp2   PCIe TX Differential signal defined by the PCIe 3.0 spression     18   3.3V   3.3V source     19   PETp2   PCIe TX Differential signal defined by the PCIe 3.0 spression     20   N/C   No connect     21   GND   Ground     22   N/C   No connect     23   PERn2   PCIe RX Differential signal defined by the PCIe 3.0 spression     23   PERn2   PCIe RX Differential signal defined by the PCIe 3.0 spression     24   N/C   No connect                                                                         | ecification  |

| 7PETp3PCle TX Differential signal defined by the PCle 3.0 spectrum8N/CNo connect9GNDGround10LED1#(O)Status indicators via LED devices11PERn3PCle RX Differential signal defined by the PCle 3.0 spectrum123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 spectrum143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 spectrum183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spectrum20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spectrum24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spectrum26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spectrum                                                                                                                                                                                                         | ecification  |

| 8N/CNo connect9GNDGround10LED1#(O)Status indicators via LED devices11PERn3PCle RX Differential signal defined by the PCle 3.0 spr123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 spr143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 spr183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spr20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spr24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spr26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spr                                                                                                                                                                                                                                                                                                              | ecification  |

| 9GNDGround10LED1#(O)Status indicators via LED devices11PERn3PCle RX Differential signal defined by the PCle 3.0 sp123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 sp143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 sp183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 sp20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 sp24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 sp                                                                                                                                                                                                                                                                                                                                   |              |

| 10LED1#(O)Status indicators via LED devices11PERn3PCle RX Differential signal defined by the PCle 3.0 sp123.3V3.3V source13PERp3PCle RX Differential signals defined by the PCle 3.0 sp143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 sp183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 sp20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 sp24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 sp                                                                                                                                                                                                                                                                                                                                             |              |

| 11PERn3PCIe RX Differential signal defined by the PCIe 3.0 sp.123.3V3.3V source13PERp3PCIe RX Differential signals defined by the PCIe 3.0 sp.143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCIe TX Differential signal defined by the PCIe 3.0 sp.183.3V3.3V source19PETp2PCIe TX Differential signal defined by the PCIe 3.0 sp.20N/CNo connect21GNDGround22N/CNo connect23PERn2PCIe RX Differential signal defined by the PCIe 3.0 sp.24N/CNo connect25PERp2PCIe RX Differential signal defined by the PCIe 3.0 sp.26N/CNo connect27GNDGround28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 sp.                                                                                                                                                                                                                                                                                                                                                                                 |              |

| 123.3V3.3V source13PERp3PCIe RX Differential signals defined by the PCIe 3.0 sp143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCIe TX Differential signal defined by the PCIe 3.0 sp183.3V3.3V source19PETp2PCIe TX Differential signal defined by the PCIe 3.0 sp20N/CNo connect21GNDGround22N/CNo connect23PERn2PCIe RX Differential signal defined by the PCIe 3.0 sp24N/CNo connect25PERp2PCIe RX Differential signal defined by the PCIe 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| 13PERp3PCle RX Differential signals defined by the PCle 3.0 sp143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 sp183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 sp20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 sp24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ecification. |

| 143.3V3.3V source15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 spe183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spe20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spe24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spe26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| 15GNDGround163.3V3.3V source17PETn2PCle TX Differential signal defined by the PCle 3.0 spectrum183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spectrum20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spectrum24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spectrum26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| 163.3V3.3V source17PETn2PCIe TX Differential signal defined by the PCIe 3.0 spectrum183.3V3.3V source19PETp2PCIe TX Differential signal defined by the PCIe 3.0 spectrum20N/CNo connect21GNDGround22N/CNo connect23PERn2PCIe RX Differential signal defined by the PCIe 3.0 spectrum24N/CNo connect25PERp2PCIe RX Differential signal defined by the PCIe 3.0 spectrum26N/CNo connect27GNDGround28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

| 17PETn2PCle TX Differential signal defined by the PCle 3.0 spectrum183.3V3.3V source19PETp2PCle TX Differential signal defined by the PCle 3.0 spectrum20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 spectrum24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 spectrum26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 183.3V3.3V source19PETp2PCIe TX Differential signal defined by the PCIe 3.0 spectrum20N/CNo connect21GNDGround22N/CNo connect23PERn2PCIe RX Differential signal defined by the PCIe 3.0 spectrum24N/CNo connect25PERp2PCIe RX Differential signal defined by the PCIe 3.0 spectrum26N/CNo connect27GNDGround28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ecification  |

| 19PETp2PCIe TX Differential signal defined by the PCIe 3.0 spectrum20N/CNo connect21GNDGround22N/CNo connect23PERn2PCIe RX Differential signal defined by the PCIe 3.0 spectrum24N/CNo connect25PERp2PCIe RX Differential signal defined by the PCIe 3.0 spectrum26N/CNo connect27GNDGround28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| 20N/CNo connect21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 sp24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ecification  |

| 21GNDGround22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 sp24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

| 22N/CNo connect23PERn2PCle RX Differential signal defined by the PCle 3.0 sp24N/CNo connect25PERp2PCle RX Differential signal defined by the PCle 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCle TX Differential signal defined by the PCle 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| 23PERn2PCIe RX Differential signal defined by the PCIe 3.0 sp24N/CNo connect25PERp2PCIe RX Differential signal defined by the PCIe 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| 24N/CNo connect25PERp2PCIe RX Differential signal defined by the PCIe 3.0 sp26N/CNo connect27GNDGround28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ecification  |

| 25     PERp2     PCIe RX Differential signal defined by the PCIe 3.0 spectrum       26     N/C     No connect       27     GND     Ground       28     N/C     No connect       29     PETn1     PCIe TX Differential signal defined by the PCIe 3.0 spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| 26   N/C   No connect     27   GND   Ground     28   N/C   No connect     29   PETn1   PCIe TX Differential signal defined by the PCIe 3.0 specified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ecification  |

| 27 GND Ground   28 N/C No connect   29 PETn1 PCIe TX Differential signal defined by the PCIe 3.0 specified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| 28N/CNo connect29PETn1PCIe TX Differential signal defined by the PCIe 3.0 specified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| 29 PETn1 PCIe TX Differential signal defined by the PCIe 3.0 spe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ecification  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| 31 PETp1 PCIe TX Differential signal defined by the PCIe 3.0 spe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ecification  |

| 32 N/C No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 33 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| 34 N/C No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 35 PERn1 PCIe RX Differential signal defined by the PCIe 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ecification  |

| 36 N/C No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 37 PERp1 PCIe RX Differential signal defined by the PCIe 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ecification  |

| 38 N/C No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 39 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| 40 SMB_CLK (I/O)(0/1.8V) SMBus Clock; Open Drain with pull-up on platform (F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reserve)     |

| 41 PETn0 PCIe TX Differential signal defined by the PCIe 3.0 spe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ecification  |

| 42 SMB_DATA (I/O)(0/1.8V) SMBus Data; Open Drain with pull-up on platform (R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

| 43 PETp0 PCIe TX Differential signal defined by the PCIe 3.0 spe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | acification  |

| 44 N/C No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Scincation   |

| 45 GND Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Scincation   |

| 46 N/C No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 47 PERn0 PCIe RX Differential signal defined by the PCIe 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| 48 N/C No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| 49 PERp0 PCIe RX Differential signal defined by the PCIe 3.0 sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ecification  |

| 50 PERST#(I)(0/3 3)() PE-Reset is a functional reset to the card as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ecification  |

| 50FERGI#(I)(0/5.5V)defined by the PCIe Mini CEM specification.51GNDGround                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ecification  |

## **AD\ANTECH**

| 52   | CLKREQ#(I/O)(0/3.3V) | Clock Request is a reference clock request signal as defined by the<br>PCIe Mini CEM specification; Also used by L1 PM Substates. |

|------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 53   | REFCLKn              | PCIe Reference Clock signals (100 MHz)                                                                                            |

| - 55 | KEFCLKII             | defined by the PCIe 3.0 specification.                                                                                            |

| 54   | PEWAKE#(I/O)(0/3.3V) | PCIe PME Wake.                                                                                                                    |

| 04   | 1 200 (0,0,0,0,0)    | Open Drain with pull up on platform; Active Low.                                                                                  |

| 55   | REFCLKp              | PCIe Reference Clock signals (100 MHz)                                                                                            |

|      |                      | defined by the PCIe 3.0 specification.                                                                                            |

| -0   | Reserved for         | Manufacturing Data line. Used for SSD manufacturing only.                                                                         |

| 56   | MFG DATA             | Not used in normal operation.                                                                                                     |

|      |                      | Pins should be left N/C in platform Socket.                                                                                       |

| 57   | GND                  | Ground                                                                                                                            |

| 50   | Reserved for MFG     | Manufacturing Clock line. Used for SSD manufacturing only.                                                                        |

| 58   | CLOCK                | Not used in normal operation.                                                                                                     |

| 50   | Madula Kau           | Pins should be left N/C in platform Socket.                                                                                       |

| 59   | Module Key           | Module Key                                                                                                                        |

| 60   | Module Key           |                                                                                                                                   |

| 61   | Module Key           |                                                                                                                                   |

| 62   | Module Key           |                                                                                                                                   |

| 63   | Module Key           |                                                                                                                                   |

| 64   | Module Key           |                                                                                                                                   |

| 65   | Module Key           |                                                                                                                                   |

| 66   | Module Key           |                                                                                                                                   |

| 67   | N/C                  | No connect                                                                                                                        |

| 68   | N/C                  | No connect                                                                                                                        |

| 69   | PEDET (NC-PCIe)      | Host I/F Indication; No Connect for PCIe.                                                                                         |

| 70   | 3.3V                 | 3.3V source                                                                                                                       |

| 71   | GND                  | Ground                                                                                                                            |

| 72   | 3.3V                 | 3.3V source                                                                                                                       |

| 73   | GND                  | Ground                                                                                                                            |

| 74   | 3.3V                 | 3.3V source                                                                                                                       |

| 75   | GND                  | Ground                                                                                                                            |

## 7. NVMe Command List

#### Admin commands

| Opcode  | Command Description         |

|---------|-----------------------------|

| 00h     | Delete I/O Submission Queue |

| 01h     | Create I/O Submission Queue |

| 02h     | Get Log Page                |

| 04h     | Delete I/O Completion Queue |

| 05h     | Create I/O Completion Queue |

| 06h     | Identify                    |

| 08h     | Abort                       |

| 09h     | Set Features                |

| 0Ah     | Get Features                |

| 0Ch     | Asynchronous Event Request  |

| 10h     | Firmware Activate           |

| 11h     | Firmware Image Download     |

|         | I/O Command Set Specific    |

| 80h     | Format NVM                  |

| 81h     | Security Send               |

| 82h     | Security Receive            |

| 83h-BFh | I/O Command Set specific    |

|         | Vendor Specific             |

| C0h-FFh | Vendor specific             |

#### NVM commands

| Opcode          | Command Description  |

|-----------------|----------------------|

| 00h             | Flush                |

| 01h             | Write                |

| 02h             | Read                 |

| 04h             | Write Uncorrectable  |

| 05h             | Compare              |

| 08h             | Write Zeroes         |

| 09h             | Dataset Management   |

| 0Dh             | Reservation Register |

| 0Eh             | Reservation Report   |

| 11h             | Reservation Acquire  |

| 15h             | Reservation Release  |