# 3 Amp $V_{TT}$ Termination Source / Sink Regulator for DDR, DDR-2, DDR-3, DDR-4

The NCP51510 is a source/sink Double Data Rate (DDR) termination regulator specifically designed for low input voltage and low-noise systems where space is a key consideration. The NCP51510 maintains a fast transient response and only requires a minimum  $V_{TT}$  load capacitance of 10 µF for output stability. The NCP51510 supports remote sensing and all power requirements for DDR  $V_{TT}$  bus termination. The NCP51510 can also be used in low-power chipsets and graphics processor cores that require dynamically adjustable output voltages. The NCP51510 is available in the thermally-efficient DFN10 Exposed Pad package, and is rated both Green and Pb-Free.

## Features

- Generate DDR Memory Termination Voltage (V<sub>TT</sub>)

- For DDR, DDR-2, DDR-3 and DDR-4 Source / Sink Currents

- Supports Loads Up to ±3 A (Typ), Output is Over-Current Protected

- Integrated MOSFETs with Thermal Shutdown Protection

- Fast Load–Transient Response

- PGOOD Output Pin to Monitor Status of VTT Output Regulation

- $\overline{SS}$  Input Pin for Suspend Shutdown mode

- V<sub>RI</sub> Input Reference for Flexible Voltage Tracking

- V<sub>TTS</sub> Input for Remote Sensing (Kelvin Connection)

- Built-in Soft-Start, Under Voltage Lockout

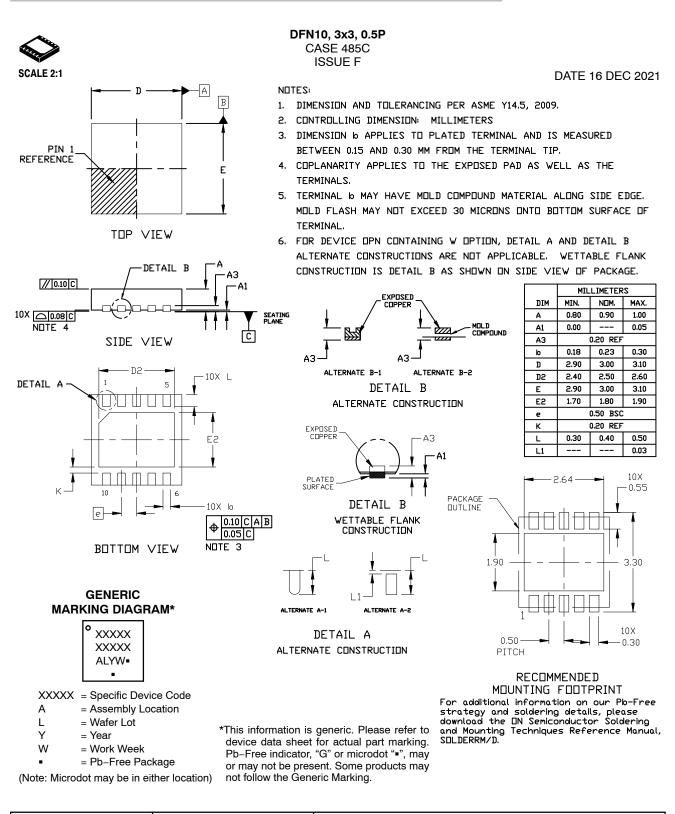

- Small, Low–Profile 10–pin, 3 x 3 mm DFN Package

- NCV51510MWTAG Wettable Flank Option for Enhanced Optical Inspection

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP Capable\*

- This is a Pb–Free Device

## Applications

- DDR Memory Termination

- Desktop PC's, Notebooks, and Workstations

- Servers and Networking equipment

- Telecom/Datacom, GSM Base Station

- Graphics Processor Core Supplies

- Set Top Boxes, LCD-TV/PDP-TV, Copier/Printers

- Supplies Power for Chipset/RAM as Low as 0.5 V

- Active Source/Sink Bus Termination

## **ON Semiconductor®**

www.onsemi.com

## MARKING DIAGRAM

(Note: Microdot may be in either location)

## **ORDERING INFORMATION**

| Device         | Package            | Shipping <sup>†</sup> |

|----------------|--------------------|-----------------------|

| NCP51510MNTAG  | _                  |                       |

| NCV51510MNTAG* | DFN10<br>(Pb–Free) | 3000 / Tape &<br>Reel |

| NCV51510MWTAG* | (1.5.1100)         |                       |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

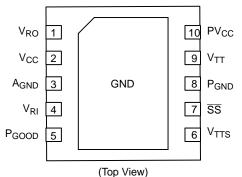

#### **PIN FUNCTION DESCRIPTION**

| Pin Number | Pin Name          | Pin Function                                                                                                                                                              |

|------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>RO</sub>   | OUTPUT – Buffered Output of V <sub>RI</sub> Reference Input pin.                                                                                                          |

| 2          | V <sub>CC</sub>   | INPUT – Regulator Analog Power Input pin. Connect to the system supply voltage. Bypass V <sub>CC</sub> to A <sub>GND</sub> with a 1 $\mu$ F or greater ceramic capacitor. |

| 3          | A <sub>GND</sub>  | Analog Ground                                                                                                                                                             |

| 4          | V <sub>RI</sub>   | INPUT – External Reference Input for V <sub>TT</sub> Output (see Figure 1 for typical application)                                                                        |

| 5          | P <sub>GOOD</sub> | OUTPUT – V <sub>TT</sub> "Power Good" pin (open drain output)                                                                                                             |

| 6          | V <sub>TTS</sub>  | INPUT – Remote Sense Input for $V_{TT}$ . The $V_{TTS}$ pin provides accurate remote feedback sensing of the $V_{TT}$ output.                                             |

| 7          | SS                | INPUT – Suspend Shutdown Control Input. CMOS compatible. Logic HIGH = enable,<br>logic LOW = shutdown. Connect to VDDQ for normal operation.                              |

| 8          | P <sub>GND</sub>  | Power Ground. Internally connected to Low-side MOSFET                                                                                                                     |

| 9          | V <sub>TT</sub>   | OUTPUT – Regulated Power Output pin                                                                                                                                       |

| 10         | PV <sub>CC</sub>  | INPUT – Regulator Power Input pin. Internally connected to High-side MOSFET                                                                                               |

| -          | THERMAL<br>PAD    | Pad for thermal connection. The exposed pad must be connected to the ground plane using multiple vias for maximum power dissipation performance.                          |

### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                          |                  |                                  | Value                            | Unit |

|-----------------------------------------------------------------|------------------|----------------------------------|----------------------------------|------|

| PV <sub>CC</sub> to P <sub>GND</sub>                            | (Note 1)         | -                                | -0.3 to 4.3                      |      |

| V <sub>CC</sub> to A <sub>GND</sub>                             | V <sub>CC</sub>  | -0.3 to 4.3                      |                                  |      |

| $V_{RI}$ , $V_{RO}$ , $\overline{SS}$ , $P_{GOOD}$ to $A_{GND}$ | (Note 1)         | -                                | –0.3 to (V <sub>CC</sub> + 0.3)  | v    |

| V <sub>TT</sub> to P <sub>GND</sub>                             | (Note 1)         | -                                | –0.3 to (PV <sub>CC</sub> + 0.3) | Ī    |

| V <sub>TTS</sub> to A <sub>GND</sub>                            | V <sub>TTS</sub> | –0.3 to (PV <sub>CC</sub> + 0.3) | 1                                |      |

| P <sub>GND</sub> to A <sub>GND</sub>                            |                  |                                  | -0.3 to +0.3                     | 1    |

| Storage Temperature                                             |                  |                                  | -65 to 150                       | °C   |

| Operating Junction Temperature Range                            |                  |                                  | -40 to 125                       |      |

| ESD Capability, Human Body Model                                | (Note 2)         | ESD <sub>HBM</sub>               | 2000                             | V    |

| ESD Capability, Machine Model (Note 2)                          |                  | ESD <sub>MM</sub>                | 200                              | V    |

| V <sub>TT</sub> Output Continuous RMS Current                   | 100 sec          | -                                | ±1.6                             | A    |

|                                                                 | 1 sec            |                                  | ±2.5                             | A    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115) Latchup Current Maximum Rating tested per JEDEC standard: JESD78.

## **DISSIPATION RATINGS**

| Package    | T <sub>A</sub> =70°C Power Rate | Derating Factor Above T <sub>A</sub> = 70°C |  |  |

|------------|---------------------------------|---------------------------------------------|--|--|

| 10–Pin DFN | 1951 mW                         | 24.4 mW / °C                                |  |  |

## **RECOMMENED OPERATING CONDITIONS**

| Rating                                       | Symbol                            | Value                | Unit |  |

|----------------------------------------------|-----------------------------------|----------------------|------|--|

| V <sub>TT</sub> Output Voltage Range         | V <sub>TT,</sub> V <sub>TTS</sub> | 0.5 to 1.5           |      |  |

| PV <sub>CC</sub> Input Voltage Range (Power) | PV <sub>CC</sub>                  | 1.1 to 3.6           | V    |  |

| V <sub>CC</sub> Input Voltage Range (Analog) | V <sub>CC</sub>                   | 2.7 to 3.6           | v    |  |

| Logic Voltage Range                          | SS, P <sub>GOOD</sub>             | 0 to V <sub>CC</sub> |      |  |

| Operating Ambient Temperature Range          | T <sub>A</sub>                    | -40 to +125          | °C   |  |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

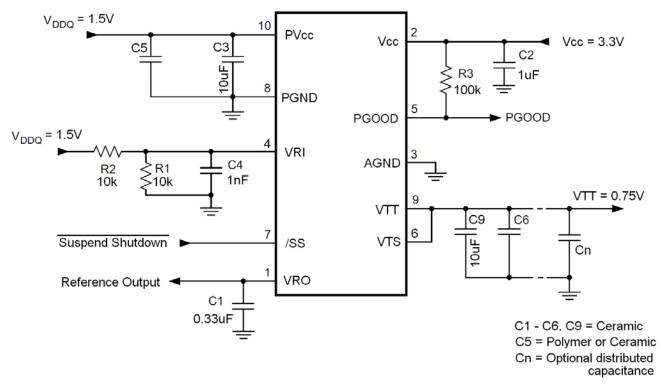

$PV_{CC} = 1.8 \text{ V}; \text{ } V_{CC} = 3.3 \text{ V}; \text{ } V_{RI} = \text{ } V_{TTS} = 1.25 \text{ V}; \text{ } \overline{SS} = \text{ } V_{CC}; \text{ (circuit of Figure 1, -40°C } \leq (\text{T}_{J} = \text{T}_{A}) \leq 125^{\circ}\text{C}; \text{ unless otherwise noted.} \text{ Typical values are at } \text{T}_{A} = +25^{\circ}\text{C}$

| Parameter                                                | Conditions                                                                                   |                                                            | Symbol                   | Min                    | Тур             | Max                    | Unit |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------|------------------------|-----------------|------------------------|------|

| OUTPUT                                                   | •<br>•                                                                                       |                                                            |                          | -                      |                 | -                      |      |

| V <sub>TT</sub> Output Voltage Range                     | $PV_{CC} > (V_{TT} + V_{DROPOUT})$                                                           |                                                            | V <sub>TT</sub>          | 0.5                    |                 | 1.5                    | V    |

| V <sub>TT</sub> Load Regulation                          | –1 A                                                                                         | ≤ I <sub>TT</sub> ≤ +1 A                                   | $\Delta V_{LOAD}$        | -4                     |                 | +4                     | mV   |

| V <sub>TT</sub> Line–Regulation                          | $1.4 \text{ V} \le \text{PV}_{\text{CC}} \le$                                                | 3.3 V, I <sub>OUT</sub> = ±100 mA                          | $\Delta V_{\text{LINE}}$ |                        | 1               |                        |      |

| Feedback–Voltage Error                                   | V <sub>RI</sub> to V <sub>TTS</sub> ,<br>I <sub>TT</sub> = ±200 mA                           | $T_A = -40^{\circ}C$ to $125^{\circ}C$                     | V <sub>TTS</sub>         | -17                    |                 | +17                    |      |

| V <sub>TT</sub> Current Slew Rate                        | C <sub>OUT</sub> = 100 լ                                                                     | μF, I <sub>TT</sub> = 0.1 A to 2 A                         | I <sub>TT</sub> di/dt    |                        | 3               |                        | A/μs |

| V <sub>TT</sub> Output Power–Supply Rejec-<br>tion Ratio | 10 Hz < f < 10<br>C <sub>OU</sub>                                                            | 0 kHz, I <sub>TT</sub> = 200 mA,<br><sub>JT</sub> = 100 μF | PSRR                     |                        | 80              |                        | dB   |

| V <sub>TT</sub> Output MOSFET R <sub>DS(on)</sub>        | High-side (sou                                                                               | urce) (I <sub>TT</sub> = +100 mA)                          | R <sub>DS(on)</sub>      |                        | 140             | 250                    | mΩ   |

|                                                          | Low-side (si                                                                                 | nk) (I <sub>TT</sub> = –100 mA)                            |                          |                        | 140             | 250                    |      |

| V <sub>TT</sub> Output-to-V <sub>TTS</sub> Input         | Internal Fee                                                                                 | edback Resistance                                          | R <sub>FB</sub>          |                        | 12              |                        | kΩ   |

| Discharge MOSFET R <sub>DS(on)</sub>                     | $\overline{SS} = 0 V$                                                                        |                                                            | R <sub>DIS</sub>         |                        | 8               |                        | Ω    |

| SUPPLY CURRENT                                           |                                                                                              |                                                            |                          |                        |                 |                        |      |

| Quiescent PV <sub>CC</sub> Current                       | No Load                                                                                      |                                                            | I <sub>PVCC</sub>        |                        | 0.4             | 10                     | mA   |

| Quiescent V <sub>CC</sub> Current                        | V <sub>RI</sub> > 0.45 V, No Load                                                            |                                                            | I <sub>CC</sub>          |                        | 0.7             | 1.3                    |      |

| Shutdown PV <sub>CC</sub> Current                        | <u>SS</u> = 0 V                                                                              |                                                            | I <sub>PVCC SD</sub>     |                        | 0.1             | 10                     | μΑ   |

| Shutdown V <sub>CC</sub> Current                         | <del>SS</del> =                                                                              | $\overline{SS} = 0V, V_{RI} = 0V$                          |                          |                        | 50              | 100                    |      |

|                                                          | <del>SS</del> = 0V, V <sub>RI</sub> > 0.45 V                                                 |                                                            |                          |                        | 350             | 600                    |      |

| REFERENCE                                                |                                                                                              |                                                            |                          |                        |                 |                        |      |

| V <sub>RI</sub> Input Voltage Range                      |                                                                                              |                                                            | V <sub>RI</sub>          | 0.5                    |                 | 1.5                    | V    |

| V <sub>RI</sub> Input–Bias current                       | T <sub>A</sub>                                                                               | , = +25°C                                                  | I <sub>RI</sub>          | -1                     |                 | +1                     | μΑ   |

| V <sub>RO</sub> Output Voltage                           | $V_{CC} = 3.3 \text{ V}, \text{ I}_{RO} = 0$                                                 |                                                            | V <sub>RO</sub>          | V <sub>RI</sub><br>–10 | V <sub>RI</sub> | V <sub>RI</sub><br>+10 | mV   |

| V <sub>RO</sub> Load Regulation                          | I <sub>RO</sub> = ±5 mA                                                                      |                                                            | $\Delta V_{RO}$          | -20                    |                 | +20                    |      |

| SUSPEND SHUTDOWN                                         |                                                                                              |                                                            |                          |                        |                 |                        |      |

| SS – Suspend Shutdown Logic                              | SS Logic HI (V <sub>TT</sub> Output Enabled)                                                 |                                                            | V <sub>IH</sub>          | 2.0                    |                 |                        | V    |

| Input Threshold                                          | SS Logic LOW (V <sub>TT</sub> Suspended)                                                     |                                                            | V <sub>IL</sub>          |                        |                 | 0.8                    |      |

| SS – Logic Input Current                                 | $\overline{SS} = V_{CC} \text{ or } 0 \text{ V},  \text{T}_{\text{A}} = +25^{\circ}\text{C}$ |                                                            | I <sub>SS</sub>          | –1                     |                 | +1                     | μΑ   |

| FAULT CONDITION - CURRENT L                              | ІМІТ                                                                                         |                                                            |                          |                        |                 |                        |      |

| Current–Limit Threshold                                  | $T_A = -40^{\circ}C$ to $+125^{\circ}C$                                                      |                                                            | I <sub>TT LIMIT</sub>    | 1.8                    | 3               | 4.2                    | А    |

| Soft-start Current-limit time                            |                                                                                              |                                                            | T <sub>SS</sub>          |                        | 200             |                        | μs   |

## **ELECTRICAL CHARACTERISTICS**

| Parameter                              | Conditions                                                                                     | Symbol                   | Min  | Тур  | Max  | Unit |

|----------------------------------------|------------------------------------------------------------------------------------------------|--------------------------|------|------|------|------|

| FAULT CONDITION - UNDER-VO             | LTAGE LOCKOUT                                                                                  |                          |      | -    |      |      |

| V <sub>CC</sub> UVLO Threshold         | Wake-up, rising edge                                                                           | V <sub>CC UVLO</sub>     | 2.50 | 2.70 | 2.90 | V    |

|                                        | Hysteresis Voltage                                                                             | -                        |      | 100  |      | mV   |

| PV <sub>CC</sub> UVLO Threshold        | Wake-up, rising edge                                                                           | PV <sub>CC</sub><br>UVLO |      | 0.9  | 1.1  | V    |

|                                        | Hysteresis Voltage                                                                             | -                        |      | 55   |      | mV   |

| V <sub>RI</sub> UVLO Voltage           | V <sub>RI</sub> , rising edge                                                                  | V <sub>RI UVLO</sub>     |      | 350  | 450  |      |

|                                        | Hysteresis Voltage                                                                             | -                        |      | 50   |      |      |

| FAULT CONDITION - THERMAL              | SHUTDOWN                                                                                       |                          |      |      |      |      |

| Thermal Shutdown Temperature           | Thermal Shutdown, rising edge                                                                  | T <sub>SD</sub>          |      | 165  |      | °C   |

| Thermal Shutdown Hysteresis            | Hysteresis Temperature                                                                         | T <sub>SH</sub>          |      | 15   |      |      |

| FAULT CONDITION - POWER GO             | OD                                                                                             |                          |      |      |      |      |

| P <sub>GOOD</sub> Lower trip threshold | With respect to feedback threshold,                                                            | -                        | -200 | -150 | -100 | mV   |

| P <sub>GOOD</sub> Upper trip threshold | hysteresis = 12 mV                                                                             | -                        | 100  | 150  | 200  |      |

| P <sub>GOOD</sub> Output Low Voltage   | I <sub>SINK</sub> = 4 mA (P <sub>GOOD</sub> MOSFET = On)                                       | -                        |      |      | 300  |      |

| P <sub>GOOD</sub> start–up delay       | Start-up rising edge, V <sub>TTS</sub> within ±100 mV<br>of the feedback threshold             | -                        | 1    | 2    | 3.5  | ms   |

| P <sub>GOOD</sub> Propagation Delay    | V <sub>TTS</sub> forced 25 mV beyond P <sub>GOOD</sub> trip<br>threshold                       | T <sub>PGOOD</sub>       | 5    | 10   | 35   | μs   |

| P <sub>GOOD</sub> Leakage Current      | $V_{TTS} = V_{RI} (P_{GOOD} Hi-impedance),$<br>$P_{GOOD} = V_{CC} + 0.3 V, T_A = +25^{\circ}C$ | I <sub>PGOOD</sub>       |      |      | 1    | μΑ   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

## General\*

The NCP51510 is a source/sink tracking termination regulator specifically designed for low input voltage and low external component count systems where space is a key application parameter. The NCP51510 integrates a high-performance, low-dropout (LDO) linear regulator that is capable of both sourcing and sinking current. The LDO regulator employs a fast feedback loop so that small ceramic capacitors can be used to support the fast load transient response. To achieve tight regulation with minimum effect of trace resistance, a remote sensing input (V<sub>TTS</sub>) should be connected to the positive terminal of the output capacitors as a separate trace from the high current path of the V<sub>TT</sub> output.

## **Generation of Internal Voltage Reference**

The V<sub>TT</sub> output voltage is regulated to (and tracks with) the voltage on the V<sub>RI</sub> Reference input. When the V<sub>RI</sub> input is configured for standard DDR termination applications, the V<sub>RI</sub> Reference input can be set by an external equivalent ratio voltage divider connected to the memory supply bus (V<sub>DDQ</sub>). The NCP51510 supports V<sub>TT</sub> voltages from 0.5 V to 1.5 V.

## **Generation of Internal Voltage Reference (cont)**

When the V<sub>RO</sub> output is configured for DDR termination applications, it provides a separate V<sub>TT</sub> output reference voltage for the memory application. The V<sub>RO</sub> Reference Output pin is a buffered version of the V<sub>RI</sub> Reference Input, and is capable of sourcing and sinking a load of ±5 mA. The V<sub>RO</sub> output becomes active when the V<sub>RI</sub> input > 0.45 V and the V<sub>CC</sub> power rail is above the UVLO threshold. The V<sub>RO</sub> Reference Output is independent of the  $\overline{SS}$  pin (Suspend Shutdown) state.

## Fault Detection and Shutdown Function

When the  $\overline{SS}$  "Suspend Shutdown" input pin is driven high, the NCP51510 regulator begins normal operation, with the Soft Start circuit gradually increasing output current during the first 200 µs in order to reduce the input surge currents at startup, with full current available after the  $200 \ \mu s$  Soft–Start circuitry has timed out.

When the  $\overline{SS}$  input is driven low, the V<sub>TT</sub> output is discharged to P<sub>GND</sub> through an internal 8  $\Omega$  MOSFET. The V<sub>RO</sub> output remains on when the  $\overline{SS}$  input is driven low. The NCP51510 provides an open–drain P<sub>GOOD</sub> "Power Good" output that goes high when the V<sub>TTS</sub> Sense input is within ±150 mV of the V<sub>RI</sub> Reference Input. The P<sub>GOOD</sub> output de–asserts within 10  $\mu$ s after the V<sub>TTS</sub> Sense input exceeds the size of the P<sub>GOOD</sub> window. During initial V<sub>TT</sub> startup, P<sub>GOOD</sub> asserts high 2 ms after the V<sub>TTS</sub> Sense input enters P<sub>GOOD</sub> window. Because the P<sub>GOOD</sub> output is open–drain, an external pull–up resistor is required (100 k $\Omega^*$ ) between P<sub>GOOD</sub> and a stable active supply voltage rail.

## Thermal Shutdown with Hysteresis

If the NCP51510 is to operate in elevated temperatures for long durations, care should be taken to ensure that the maximum operating junction temperature is not exceeded. To guarantee safe operation, the NCP51510 provides on-chip thermal shutdown protection. When the chip junction temperature exceeds  $165^{\circ}C^{*}$ , the part will shutdown. When the junction temperature falls back, to  $150^{\circ}C^{*}$ , the device resumes normal operation. If the junction temperature exceeds the thermal shutdown threshold, the V<sub>TT</sub> output is shut off, discharged by the 8  $\Omega$ internal discharge MOSFET.

## **Output Capacitor**

Output stability is guaranteed for  $V_{TT}$  output capacitance  $C_{OUT}$  from 10  $\mu$ F to 220  $\mu$ F. The ESR of  $C_{OUT}$  between 2 m $\Omega$  and 50 m $\Omega$  is required to maintain stability. Use the formula below to calculate the application's transient response:

$$\Delta I_{TT(pp)} \times ESR = \Delta V_{TT(pp)}$$

Where:

$\Delta I_{TT(pp)}$  is the maximum peak–to–peak load current delta and  $\Delta V_{TT(pp)}$  is the allowable peak–to–peak voltage tolerance.

\*Typical values are used with the application description text. Please refer to the Electrical Specifications Table for a more detailed list of MIN, MAX and TYPICAL values.

Figure 1. Standard Application Schematic for NCP51510

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98AON03161D | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION: DFN10, 3X3 MM, 0.5 MM PITCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                                                                                                                                                                                   |  |  |  |  |

| onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation |             |                                                                                                                                                                                   |  |  |  |  |

special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

© Semiconductor Components Industries, LLC, 2019

DUSEM

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative